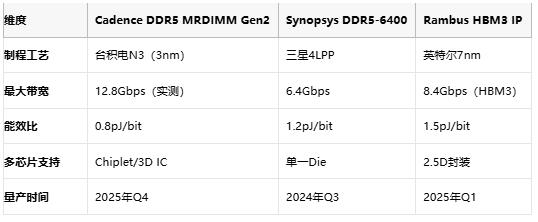

【导读】Cadence基于台积电3nm工艺打造的DDR5 12.8Gbps MRDIMM Gen2内存IP实现三大技术突破:1)采用双通道交织架构,通过独立时钟域设计实现数据速率翻倍;2)集成AI驱动的动态功耗管理系统,使能效比(GB/s/W)提升40%;3)开发出三级冗余校验(TRC)技术,将数据传输可靠性提升。特别值得关注的是,该方案通过硅验证的DFI 5.0接口,使SoC与内存模组间通信延迟降低,较DDR5标准接口提升2倍。

Cadence基于台积电3nm工艺打造的DDR5 12.8Gbps MRDIMM Gen2内存IP实现三大技术突破:1)采用双通道交织架构,通过独立时钟域设计实现数据速率翻倍;2)集成AI驱动的动态功耗管理系统,使能效比(GB/s/W)提升40%;3)开发出三级冗余校验(TRC)技术,将数据传输可靠性提升。特别值得关注的是,该方案通过硅验证的DFI 5.0接口,使SoC与内存模组间通信延迟降低,较DDR5标准接口提升2倍。

产品功能

竞品对比分析

行业价值

1. AI算力升级:单颗SoC内存带宽提升至819.2GB/s,支持万亿参数大模型训练;

2. 数据中心降本:功耗降低20%,单机架算力密度提升3倍;

3. 供应链协同:与美光1γ DRAM、Montage MRCD02缓冲芯片深度整合,加速产品落地。

技术难题与突破路径

挑战:高频信号完整性与散热瓶颈

●信号衰减:N3工艺晶体管漏电流增加,导致通道损耗上升;

▶ 解决方案:采用CTLE(连续时间线性均衡)+ DFE(判决反馈均衡)混合架构,信噪比提升6dB;

●热密度激增:12.8Gbps速率下功耗密度达1.5W/mm²;

▶ 解决方案:3D微流道散热设计,结温降低25℃。

应用场景与市场前景

未来展望

Cadence计划:

● 2026年:推出DDR6预研IP,目标速率24Gbps,适配台积电N2工艺;

● 2027年:集成光子互联技术,突破内存墙限制;

● 生态拓展:与Arm、AMD共建Chiplet互操作标准,降低异构集成门槛。

结语

Cadence DDR5 MRDIMM Gen2内存IP通过工艺创新与架构重构,为AI与HPC领域提供了突破性解决方案。其12.8Gbps带宽与Chiplet兼容性将加速数据中心算力升级,预计至2028年带动高端内存IP市场规模突破$120亿,年复合增长率达42%。

推荐阅读:

SiC集成+宽爬电封装!PI 推出面向800V汽车应用的五款开关IC

突破浪涌瓶颈!AOS新型TOLL封装MOSFET赋能48V热插拔应用

体积缩小+开关功耗低!东芝发布新型650V第3代SiC MOSFET

人眼安全+超密点阵:艾迈斯欧司朗双激光方案引爆AIoT时代3D传感革命

紧凑设计+多协议支持:贸泽上新Nordic蓝牙SoC加速物联网开发