【导读】20 年来首桩晶体管接点与导线的重大金属材料变革,能解除 7 纳米及以下晶圆工艺主要的效能瓶颈,由于钨(W)在晶体管接点的电性表现与铜(Cu)的局部终端金属导线工艺都已逼近物理极限……

半导体设备商应用材料(Applied Materials)日前宣布,材料工程获得技术突破,能在大数据与人工智能(AI)时代加速芯片效能。应用材料表示,20 年来首桩晶体管接点与导线的重大金属材料变革,能解除 7 纳米及以下晶圆工艺主要的效能瓶颈,由于钨(W)在晶体管接点的电性表现与铜(Cu)的局部终端金属导线工艺都已逼近物理极限,成为 FinFET 无法完全发挥效能的瓶颈,因此芯片设计者在 7 纳米以下能以钴(Co)金属取代钨与铜,藉以增进 15% 芯片效能。

采用钴可优化先进工艺金属填充情形,延续 7 纳米以下工艺微缩

钨和铜是目前先进工艺采用的重要金属材料,然而钨和铜与绝缘层附着力差,因此都需要衬层(Liner Layer)增加金属与绝缘层间的附着力;此外,为了避免阻止钨及铜原子扩散至绝缘层而影响芯片电性,必须有障壁层(Barrier Layer)存在。

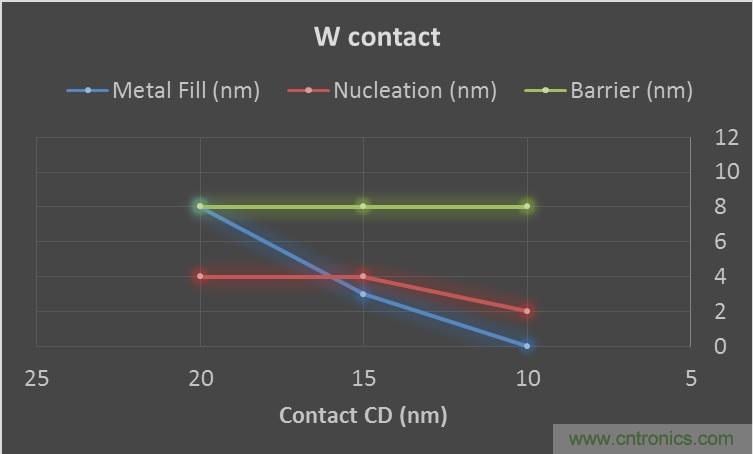

如下图所示,随着工艺微缩至 20 纳米以下,以钨 Contact(金属导线及晶体管间的连接通道称为 Contact,由于 Contact 实际形状为非常贴近圆柱体的圆锥体,因此 Contact CD 一般指的是 Contact 直径)工艺为例,20 纳米的 Contact CD 中,Barrier 就占 8 纳米,Contact 中实际金属层为 12 纳米(Metal Fill 8nm+Nucleation 4nm),Contact CD 为 10 纳米时,实际金属层仅剩 2 纳米,以此估算 Contact CD 为 8 纳米时将没有金属层的容纳空间,此时衬层及障壁层的厚度成了工艺微缩瓶颈。

钨 Contact 的 metal fill 情形。(Source:应用材料;整理:拓墣产研)

注:图中 Barrier 包含衬层+障壁层。

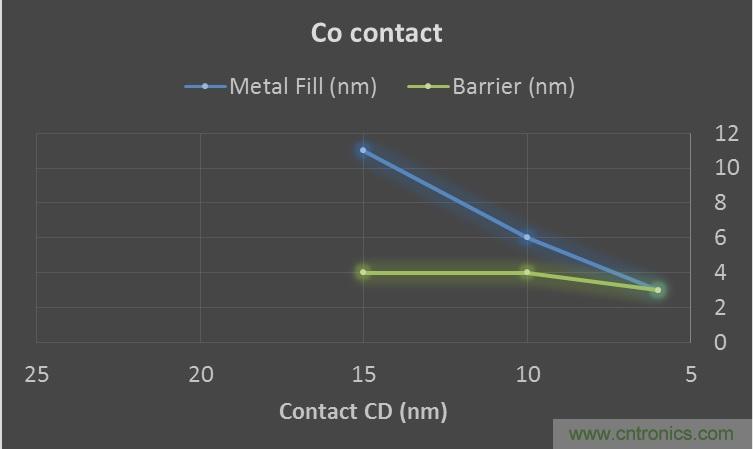

然而同样 10 纳米的 Contact CD 若采用钴(如下图),其障壁层仅 4 纳米,而实际金属层有 6 纳米,相较于采用钨更有潜力在 7 纳米以下工艺持续发展。

钴 Contact 的 metal fill 情形。(Source:应用材料;整理:拓墣产研)

注:图中 Barrier 包含衬层+障壁层。

金属材料变革将影响中国半导体设备的研发方向

目前中国半导体设备以蚀刻、薄膜及 CMP 发展脚步最快,此部分将以打入主流厂商产线、取得认证并藉此建立量产数据为目标,朝向打入先进工艺的前段晶体管工艺之远期目标相当明确,然而相较国际主流半导体设备厂商的技术水平,中国半导体设备厂商仍是追随者角色,因此钴取代钨和铜的趋势确立,将影响中国半导体设备厂商尤其是蚀刻、薄膜及 CMP 的研究发展方向。

推荐阅读: