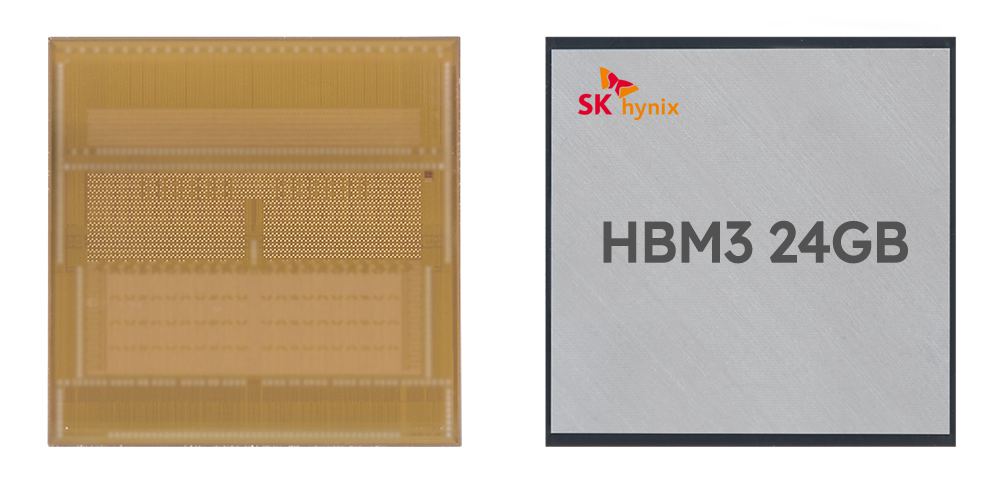

【导读】SK海力士(或‘公司’)20日宣布,再次超越了现有最高性能DRAM(内存)——HBM3*的技术界限,全球首次实现垂直堆叠12个单品DRAM芯片,成功开发出最高容量24GB(Gigabyte,千兆字节)**的HBM3 DRAM新产品,并正在接受客户公司的性能验证。

· 成功开发目前最高容量24GB HBM3 DRAM产品,正进行客户验证

· 世界上首次垂直堆叠12个单品DRAM芯片,实现高容量、高性能

· 将在上半年内完成量产准备,“加强尖端DRAM市场主导权”

2023年4月20日 – SK海力士(或‘公司’)20日宣布,再次超越了现有最高性能DRAM(内存)——HBM3*的技术界限,全球首次实现垂直堆叠12个单品DRAM芯片,成功开发出最高容量24GB(Gigabyte,千兆字节)**的HBM3 DRAM新产品,并正在接受客户公司的性能验证。

*HBM(High Bandwidth Memory):垂直连接多个DRAM,与DRAM相比显著提升数据处理速度的高附加值、高性能产品。HBM DRAM产品以HBM(第一代)、HBM2(第二代)、HBM2E(第三代)、HBM3(第四代)的顺序开发。

**现有HBM3 DRAM的最大容量是垂直堆叠8个单品DRAM芯片的16GB。

SK海力士强调“公司继去年6月全球首次量产HBM3 DRAM后,又成功开发出容量提升50%的24GB套装产品。”,“最近随着人工智能聊天机器人(AI Chatbot)产业的发展,高端存储器需求也随之增长,公司将从今年下半年起将其推向市场,以满足市场需求。”

公司技术团队在此次此新产品采用了先进(Advanced)MR-MUF*和TSV**技术。SK海力士表示,通过先进MR-MUF技术加强了工艺效率和产品性能的稳定性,又利用TSV技术将12个比现有芯片薄40%的单品DRAM芯片垂直堆叠,实现了与16GB产品相同的高度。

*MR-MUF:将半导体芯片堆叠后,为了保护芯片和芯片之间的电路,在其空间中注入液体形态的保护材料,并固化的封装工艺技术。与每堆叠一个芯片时,铺上薄膜型材料的方式对比工艺效率高,散热方面也更有效。

**TSV(Through Silicon Via, 硅通孔技术)在DRAM芯片打上数千个细微的孔,并通过垂直贯通的电极连接上下芯片的先进封装(Advanced Packaging)技术。采用该技术的SK海力士HBM3 DRAM可每秒传输163部全高清(Full-HD)电影,最大速度可达819GB/s(每秒819千兆字节)。

SK海力士于2013年在世界上首次开发的HBM DRAM是实现需要高性能计算的生成式AI所必要的存储器半导体产品,因此在受到业界的高度关注。

最新规格的HBM3 DRAM被评价为能够快速处理庞大数据的首选产品,从而大型科技公司的需求也在逐渐扩大。

公司已向数多全球客户公司提供了24GB HBM3 DRAM样品正在进行性能验证,据悉客户对此产品抱有极大的期待。

SK海力士封装测试(P&T)担当副社长洪相后表示:“公司以全球顶级后端工艺技术力为基础,接连开发出了超高速、高容量的HBM DRAM产品。将在今年上半年内完成新产品的量产准备,以巩固人工智能时代尖端DRAM市场的主导权”

关于SK海力士

SK海力士总部位于韩国,是一家全球领先的半导体供应商,为全球客户提供DRAM(动态随机存取存储器),NAND Flash(NAND快闪存储器)和CIS(CMOS图像传感器)等半导体产品。公司于韩国证券交易所上市,其全球托存股份于卢森堡证券交易所上市。

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理。

推荐阅读:

Pickering推出新的PXI多通道电池仿真模块 — 仿真堆叠电压高达1000V

ROHM开发出具有业界超低导通电阻的Nch MOSFET,有助于提高应用设备工作效率