【导读】全球半导体封装技术即将迎来历史性转折。据产业链人士透露,台积电计划于2027年量产面板级封装(Panel-Level Packaging, PLP),将采用600mm×600mm超大载板,较现行300mm晶圆级封装面积利用率提升4倍。这一技术突破,直指2030年达1.2万亿美元的AI芯片市场,或将重塑全球封测产业竞争格局。

全球半导体封装技术即将迎来历史性转折。据产业链人士透露,台积电计划于2027年量产面板级封装(Panel-Level Packaging, PLP),将采用600mm×600mm超大载板,较现行300mm晶圆级封装面积利用率提升4倍。这一技术突破,直指2030年达1.2万亿美元的AI芯片市场,或将重塑全球封测产业竞争格局。

技术降维打击:成本与性能双杀

台积电PLP技术路线图显示,其核心突破在于:

-

成本优势:单位面积封装成本较CoWoS降低30%,可满足AI加速器芯片超2000mm²的封装需求;

-

工艺革新:采用新型激光钻孔与巨量焊接技术,实现10μm级凸点间距,支持8HBM+1逻辑芯片异构集成;

-

散热突破:集成微流道冷却系统,热阻较现有方案下降40%,攻克3D封装散热瓶颈。

(数据来源:台积电2024技术研讨会披露PLP试产良率达85%,超业界预期)

市场驱动力:AI芯片的“面积饥渴症”

当前AI芯片封装需求正以每年62%的速度狂飙:

-

算力军备竞赛:NVIDIA Blackwell GPU封装面积达1800mm²,AMD MI400X预计突破2200mm²;

-

产能缺口:台积电CoWoS产能2024年增至40万片仍供不应求,PLP量产可提升单线产能3倍;

-

成本压迫:英伟达H200封装成本占比升至28%,PLP技术或助其BOM成本下降15%。

(行业现状:Yole预测2027年先进封装市场规模将达780亿美元,PLP占比超25%)

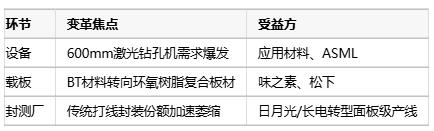

产业链地震:设备与材料商重押技术迁移

PLP技术将引发供应链深度重构:

中国变量:长电科技已组建PLP专项团队,计划2026年建成试验线;通富微电联合中科院研发自主面板级键合设备。

技术暗战:与英特尔、三星的“封装世界大战”

-

英特尔:力推EMIB+Foveros混合封装,已获AWS AI芯片大单;

-

三星:H-Cube技术聚焦HBM集成,但载板尺寸限制在500mm×500mm;

-

台积电:PLP+CoWoS-S整合方案,剑指2030年60%先进封装市占率。

(竞争态势:TechInsights数据显示,2023年台积电先进封装营收占比达34%,首次超越日月光)

风险预警:技术迁移的“死亡谷”

-

设备成熟度:600mm镀铜设备尚未通过车规认证,量产延迟风险;

-

材料瓶颈:超大载板翘曲控制需纳米级补偿技术,良率爬坡挑战;

-

生态壁垒:ARM/RISC-V架构需重构EDA工具链适配PLP设计规则。

结语

当台积电将摩尔定律的战场从晶体管微缩转向封装革命,面板级封装不仅是技术跃迁,更是半导体产业价值分配的重构。在这场颠覆战中,能否掌控PLP技术标准,将决定未来十年AI芯片帝国的权力版图。

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理。

推荐阅读:

存储芯片涨价潮再起:原厂减产+AI刚需推动Q3价格跳涨10%

IP市场狂飙20%!85亿美元背后的HPC“军备竞赛”与ARM王座危机