【导读】东芯半导体Parallel NAND Flash 兼容传统的并行接口标准,适合大数据的读写,工艺制程24nm即将实现量产。

摘要

东芯半导体Parallel NAND Flash 兼容传统的并行接口标准,适合大数据的读写,工艺制程24nm即将实现量产。

在NAND Flash领域,24nm是目前国内领先的工艺制程,东芯半导体在国内领先的24nm的工艺制程上也有突破,也即将实现量产。因此,东芯的24nm Parallel NAND Flash在访问速率及功耗都更具优势,关键技术且都具有自主专利。

产品规格:

容量:1Gb/2Gb/4Gb/8Gb

电压:1.8V/3.3V

温度:-40°C~85°C

线宽:x8/x16

速度:20ns/25ns,30ns/45ns

封装:TSOP48,VFBGA63,VFBGA67,KGD

先进工艺制程,严格产品把控

24nm先进工艺制程。缩小器件的特征尺寸,降低功耗,降低成本,提高产品竞争力。

功能上对标同类产品,合格jedec标准,接口及操作时序均一致,设置超过500项的仿真验证项,确保设计成功,可直接进行国产替代。主要产品指标比如电压,接口位宽,page size,Random access time,Page program time,data retention等也均和国际一流产品一致。通用的并行接口,MID/DID以及parameter页等设置也符合JEDEC标准,支持LEGACY/ONFI 1.0 COMMAND SET指令集,具备更好的兼容性。

多方面提高产品可靠性

东芯的24nm NAND通过自主研发使用BCH码实现ECC 8bit/512Byte功能,极大提升产品可靠性,实现了存储单元与功能单元的高度集成在同一颗芯片内,减少芯片成品面积,缩短存储数据的读写时间。

东芯设计的ECC模块可以校验高达8bit的错误数据,以512Byte大小闪存单元为例,当其中存储的数据出现错误的位数在8位及8位以下时,ECC模块可以精准识别并自动修改错误数据,大幅度提升存储芯片的容错性和可靠性。

使用高可靠性CAM模块,提高可靠性。

使用多种可选通过电压的方式,实现局部自电位升压,在编写操作时有效保护非目标单元,极大地提高产品可靠性。

低功耗下的高效访问速率

高性能的数据访问,通过内部buffer可以提供数据吞吐量,一页从存储阵列到数据寄存器小于25微秒。1.8V连续读写的时钟周期为30纳秒,而3.3V仅需20纳秒。典型的页写入时间达到200微秒。

东芯的24nm NAND不用借助外部缓冲就可以实现快速的页拷贝;独立的/WP引脚可以实现对存储数据擦/写的硬件保护。

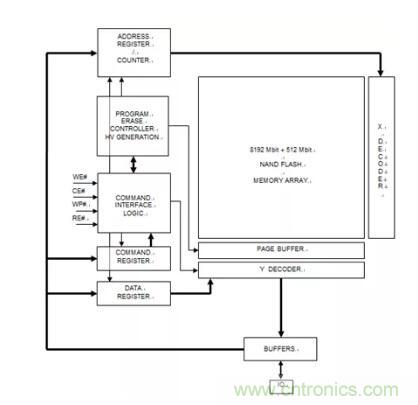

Functional block diagram如下图所示,以8Gb为例:

由此可见,标准并行通讯接口与CPU交互,并通过内部命令控制逻辑传达指令到内部,数据读取时Data register首先缓存,再通过IO送出。

同时,东芯使用独立的LDO模块分别给核心模块与电压泵模块供电,在确保供电稳定的前提下节省静待功耗。使用步进式+多次式方法进行编写/擦除操作,也对单元阈值电压精准控制。

对标最高工艺制程,不断提升性能,东芯半导体24nm Parallel NAND Flash 即将实现量产。

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请电话或者邮箱联系小编进行侵删。