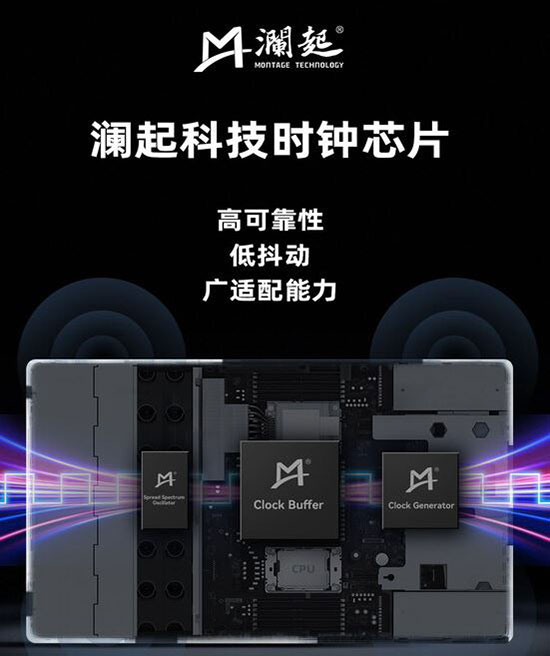

【导读】澜起科技今日宣布其高性能时钟芯片产品线全面升级,包括已量产的时钟发生器、送样阶段的时钟缓冲器和展频振荡器。该系列产品以0.3ps超低抖动和可编程输出架构,为AI服务器、5G基站等关键基础设施提供"系统级"时钟树解决方案,性能指标达到国际领先水平。

1. 技术难点及应对方案

行业痛点:

-

高速运算下时钟抖动导致数据错误

-

多设备同步精度不足

-

EMI干扰影响信号完整性

创新突破:

√ 采用混合信号PLL架构,相位噪声优化40%

√ 专利展频技术,EMI降低15dB

√ 每通道独立可编程(驱动/电压/频率)

2. 核心作用:数字系统的"心跳加速器"

-

确保AI服务器GPU/CPU同步精度(<1ns)

-

保障5G基站AAU与DU间时间同步

-

实现工业PLC多轴运动控制时序对齐

3. 产品关键竞争力(对比前代)

4. 同类竞品对比分析

-

TI LMK系列:抖动0.5ps,但缺乏展频功能

-

Silicon Labs SI5338:通道数少,价格高30%

-

核心优势:澜起实现性能、功能与成本的"黄金三角"

5. 实际应用场景

-

AI服务器:HBM内存与计算芯片时钟同步

-

5G Open RAN:分布式单元间时间对齐

-

工业机器人:16轴协同运动控制

6. 产品供货情况

-

量产:6款时钟发生器(覆盖1-4GHz)

-

送样:20款缓冲器+4款振荡器

-

交期:标准品4-6周,定制方案8周

-

7. 结语:重新定义时钟芯片价值边界

澜起科技通过这次产品线升级,不仅填补了国内高端时钟芯片空白,更以系统级思维重构了时钟解决方案。在AI与5G驱动的高速数字时代,精准时钟正从基础元件升级为关键竞争力,澜起的技术突破或将重塑产业链价值分配。

推荐阅读:

集成驱动+时序生成:东芝TCD2728DG简化高精度成像系统设计

像素级灯光控制!大联大世平推出矩阵大灯方案,刷新夜间安全标准

全封装覆盖:谷泰微GT895X系列提供SC70至TSSOP14六种封装选项

DR8架构+500米长距:环旭电子发布AI数据中心专用光模块