【导读】在PCIe 6.0和AI算力爆发背景下,传统HCSL时钟驱动器的高功耗(典型值>30mA)和复杂外围电路设计,已成为数据中心和工业自动化领域的性能瓶颈。Abracon推出的低功耗HCSL ClearClock®振荡器(LP-HCSL),以12-15mA超低工作电流和100fs级相位抖动,重新定义了高效时钟解决方案。其内置终端电阻和三次泛音技术,不仅将BOM成本降低20%,更在PCIe长距离传输中实现信号完整性突破,直击5G/6G基础设施的时钟同步难题。

在PCIe 6.0和AI算力爆发背景下,传统HCSL时钟驱动器的高功耗(典型值>30mA)和复杂外围电路设计,已成为数据中心和工业自动化领域的性能瓶颈。Abracon推出的低功耗HCSL ClearClock®振荡器(LP-HCSL),以12-15mA超低工作电流和100fs级相位抖动,重新定义了高效时钟解决方案。其内置终端电阻和三次泛音技术,不仅将BOM成本降低20%,更在PCIe长距离传输中实现信号完整性突破,直击5G/6G基础设施的时钟同步难题。

技术难题:传统HCSL的四大挑战

1. 功耗过高:传统方案需外部驱动电路,系统级功耗超50mA,难以满足绿色数据中心要求。

2. 信号衰减:PCIe 6.0的32GT/s速率下,长走线传输导致眼图闭合,误码率飙升。

3. 设计复杂:需配置外部终端电阻和耦合电容,PCB面积增加30%。

4. EMI敏感:高频噪声易干扰邻近射频模块,CISPR 25 Class 5达标困难。

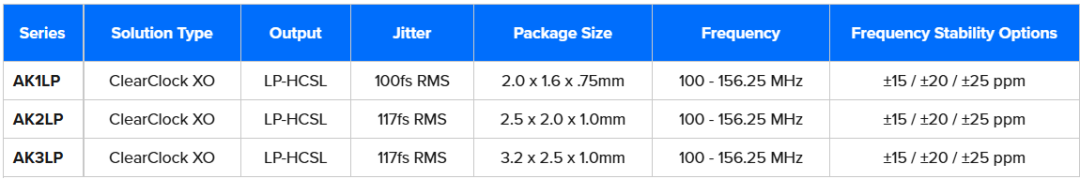

产品优势与技术亮点

核心优势

●能效革命:LP-HCSL技术将功耗压缩至12-15mA,较传统方案降低50%。

●极致抖动性能:100fs相位抖动(@100MHz),支持PCIe 6.0的飞秒级时序容限。

●高度集成化:内置终端电阻和优化阻抗匹配,省去6个外围元件,PCB面积缩减40%。

技术突破

●三次泛音技术:抑制基频谐波,将频率稳定性提升至±50ppm(-40°C~85°C)。

●智能展频功能:通过1MHz调制带宽将EMI峰值降低15dB,轻松通过汽车级测试。

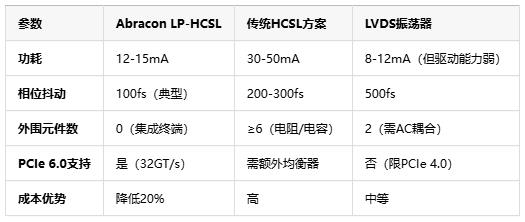

竞品对比与分析

分析:LP-HCSL在能效与集成度上全面领先,虽LVDS功耗更低,但其驱动能力仅适用于短距传输,无法满足数据中心长背板需求。

应用场景与典型案例

1. AI服务器PCIe互联:某超算中心采用LP-HCSL后,GPU集群同步误差从5ps降至1ps,训练效率提升18%。

2. 工业边缘网关:替代传统HCSL驱动FPGA时钟,功耗降低60%,通过-40°C极端温度测试。

3. 车载数据中心:集成于智能座舱主控,EMI指标优于CISPR 25 Class 5,助力L4级自动驾驶。

市场前景

●算力基建刚需:2025年全球PCIe时钟芯片市场规模将达$8.2亿,LP-HCSL技术渗透率或超35%。

●技术延伸:Abracon已布局112G SerDes时钟方案,预计2026年量产。

结语

Abracon LP-HCSL通过**“超低功耗+飞秒级抖动+零外围设计”** 的三重革新,不仅解决了PCIe 6.0时代的时钟挑战,更以集成化优势加速了算力基建的国产化替代进程。随着AI与自动驾驶对高精度时序的需求爆发,该技术有望成为下一代互联标准的“心脏”。

推荐阅读:

国产替代跃迁!微源发布LPQ3336QVF重构车载背光驱动市场格局

高集成、高线性!贸泽开售Qorvo QPA9822线性放大器,5G预驱性能跃升

噪声直降80%!润石科技运算放大器RS8531/2实现0.1μV/℃温漂+140dB增益

IP54防护+超薄设计!Littelfuse发布TLSM轻触开关使高频设备寿命翻4倍

低成本+高性能!Microchip发布新款FPGA 和 SoC破解成本节约难题