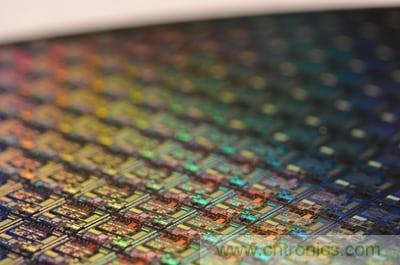

【导读】8月 26日讯,日前,台积电举办了第 26 届技术研讨会,披露了旗下最新工艺制程的进度,包括最新 5nm 工艺,以及更先进的 3nm、4nm 工艺。

8月 26日讯,日前,台积电举办了第 26 届技术研讨会,披露了旗下最新工艺制程的进度,包括最新 5nm 工艺,以及更先进的 3nm、4nm 工艺。

其实大家都知道,目前国际上芯片代工最成功的就是美国的台积电了,这也是目前唯一可以代加工 5nm 芯片的公司。从市场来看,不论是高端芯片骁龙 865 和麒麟 990,还是中低端芯片骁龙 765G 和麒麟 820 等,这些芯片都是由 7nm 工艺制造。

台积电表示,公司规划了两代 5nm 工艺,分别是 N5 和 N5P,其中 N5 引入 EUV(极紫外光刻)技术,目前已大规模量产。据说苹果 A14 和麒麟 9000 系列均使用了这项工艺打造。

按照官方的说法,相比目前旗舰 SoC 使用的 N7,N5 的功耗降低了 30%、性能提升 15%,逻辑器件密度提升了 1.8 倍。

N5P 是基于 N5 的改良版,还在开发中,规划 2021 年量产,相比第一代 5nm 功耗进一步降低 10%,且性能提升了 5%。

模拟降噪处理电路vs数字降噪处理电路

然后是更为先进的 3nm、4nm,从命名来看,4nm 是 5nm 的进一步改良,将于明年晚些时候风险试产,2022 年量产,使用 N5 的客户能够顺利过渡到 4nm,基本可以视为 5nm 的最终改良版。

这和之前 6nm 工艺有些相同,它也是 7nm 工艺的升级版,优势在于性能、功耗继续优化,同时设计上彼此兼容,客户能以几乎相同的成本拿到新工艺。

而 3nm 才是 5nm 真正的迭代升级,同样是在明年晚些时候风险试产,2022 年投入大规模量产。台积电表示,相比 5nm 工艺,3nm 将可以带来 25~30%的功耗减少以及 10~15%的性能提升。

不过台积电并不是唯一一家量产 3nm 工艺的厂商,三星此前透露明年就要把 3nm 量产安排,并且两家核心技术不尽相同,台积电使用的是 FinFET(鳍式场效应晶体管),三星则是改用 Gate-All-Around(GAA,环绕栅极晶体管),两种技术差异需等最终量产为准。

此外台积电还表示,3nm 工艺研发符合预期,并没有受到疫情影响,预计在 2021 年进入风险试产阶段,2022 年下半年量产。

工艺上,台积电评估多种选择后认为现行的 FinFET 工艺在成本及能效上更佳,所以 3nm 首发依然会是 FinFET 晶体管技术。

但台积电老对手三星则押宝 3nm 节点翻身,所以进度及技术选择都很激进,将会淘汰 FinFET 晶体管直接使用 GAA 环绕栅极晶体管。

按照三星的说法,3nm 可将核心面积减少 45%,功耗降低 50%,性能提升 35%,但需要注意的是,三星对比的是 7nm 工艺。

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请电话或者邮箱联系小编进行侵删。

IC Insights:2020年 MCU 受创最重,大跌8%

华新科将扩产滤波器及天线(LTCC)

7nm需求如此旺盛,台积电已造10亿颗,搭载产品超过100款

Q2季度全球DRAM市场规模增至171亿美元

国巨:钽电容价格年底或翻倍!