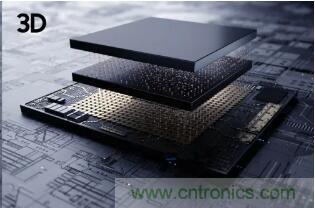

【导读】将芯片从2D平铺封装改成3D立体式堆叠式封装已经成为目前半导体业界的共识,这种在第三维度上进行拓展的封装技术能够有效降低整个芯片的面积,提升集成度。3D封装顾名思义,就是将芯片从平面堆叠变成了垂直堆叠,类似搭积木那样一层层叠加,减少了芯片面积,提高了集成度。

将芯片从2D平铺封装改成3D立体式堆叠式封装已经成为目前半导体业界的共识,这种在第三维度上进行拓展的封装技术能够有效降低整个芯片的面积,提升集成度。3D封装顾名思义,就是将芯片从平面堆叠变成了垂直堆叠,类似搭积木那样一层层叠加,减少了芯片面积,提高了集成度。

目前业界领头羊都在3D封装技术上面努力着,前有台积电的CoWoS(实际上是2.5D),后有Intel的Foveros,现在三星也公布了自家的3D封装技术,名为X-Cube。

今天,三星电子宣布,该公司的3D封装技术已经测试成功,从现在起就可用在7nm及5 nm制程。

据悉,该公司研发出的3D封装技术取名为“X-Cube”,取自英文eXtended-Cube 的缩写。

X-Cube这项3D封装技术,利用TSV 硅穿孔封装科技,可让多个芯片进行堆叠,制造出单一的逻辑芯片。

三星在7nm制程的测试过程中,成功利用TSV 技术将SRAM 堆叠在逻辑芯片顶部,这也使得在电路板的配置上,可在更小的面积上装载更多的存储单元。该3D封装的其他优点,还包含芯片间的信号传递距离更短,以及将数据传送及能量效率提升到最高。

三星电子也提到X-Cube 所带来的好处,可让芯片工程师们在进行客制化解决方案的过程中,能享有更多弹性,也更贴近他们的特殊需求。

X-Cube可灵活应用于未来芯片之上,包括5G、AI和高性能计算等领域的芯片均可使用该技术。三星表示X-Cube已经在自家的7nm和5nm制程上面通过了验证,计划和无晶圆厂的芯片设计公司继续合作,推进3D封装工艺在下一代高性能应用中的部署。三星将会在下星期的Hot Chips峰会上公布关于X-Cube的更多信息。

在三星推出X-Cube之后,全球主要的三家半导体代工厂均已经拥有3D或2.5D的封装技术了,显而易见的是,未来我们买到的电子产品中,使用3D封装技术的芯片比例会越来越高。

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请电话或者邮箱联系小编进行侵删。

订单爆满,台积电收购力特台南科技园区工厂

e络盟与KOA签订新分销协议

8寸晶圆产能吃紧 PC厂这些料缺货严重

预计2024年全球LED智慧路灯市场规模将突破10亿美元大关

中芯国际:14nm已进入量产阶段,良率提升中