【导读】知情人士称,台积电正在探索一种先进芯片封装的新方法,使用矩形面板状基板而不是传统的圆形晶圆,这将允许在每个晶圆上放置更多组芯片。

知情人士称,台积电正在探索一种先进芯片封装的新方法,使用矩形面板状基板而不是传统的圆形晶圆,这将允许在每个晶圆上放置更多组芯片。

报道称,该研究处于早期阶段,可能需要“几年”才能商业化,但它代表了台积电的重大技术转变,此前台积电认为使用矩形基板太具挑战性。

据知情人士透露,目前正在试验的矩形基板尺寸为510mm×515mm,可用面积是目前12英寸圆形晶圆的三倍多。消息人士称,矩形形状意味着边缘剩余的未使用面积会更少。

台积电先进的芯片堆叠和组装技术采用12英寸硅晶圆,这是目前最大的硅晶圆。台积电正在扩大其先进芯片封装产能,以满足不断增长的需求。据知情人士透露,中国台湾台中工厂的扩建主要是为了英伟达,而台南工厂的扩建是为了亚马逊及其芯片设计合作伙伴Alchip。

当被问及此事时,台积电表示“密切关注先进封装技术的进展和发展,包括面板级封装”。

芯片封装技术曾经被视为芯片制造中技术含量相对较低的一个领域,但如今它对于保持半导体进步的步伐已变得越来越重要。

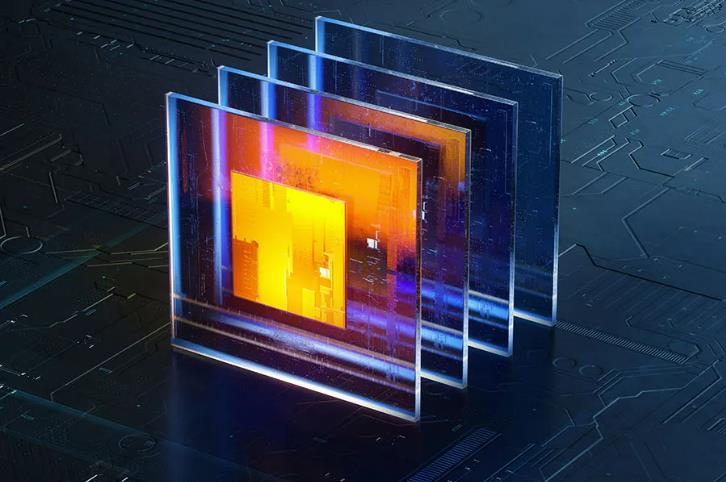

以英伟达的H200和B200等AI计算芯片为例,仅使用最先进的芯片生产是不够的,还需要采用台积电首创的先进芯片封装技术CoWoS。例如,对于B200芯片组,CoWoS可以将两个Blackwell图形处理单元组合在一起,并将它们与八个高带宽存储(HBM)芯片连接起来,从而实现快速数据吞吐量和加速计算性能。

伯恩斯坦研究公司(Bernstein Research)的半导体分析师马克·李(Mark Li)表示,台积电可能很快就需要考虑使用矩形基板,因为AI芯片组对每个封装中芯片数量的要求将越来越高。

推荐阅读: