【导读】在SoC设计中,NOR闪存的高可靠性与NAND闪存的大容量、高性价比始终难以兼顾,传统方案需采用两个独立PHY实现双协议支持,不仅增加硅片面积与引脚数量,还提升了设计复杂度与成本。如今这一行业痛点迎来解决方案——领先的移动和汽车SoC半导体IP提供商Arasan Chip Systems正式推出xSPI + eMMC组合PHY IP,将xSPI与eMMC 5.1 PHY融合于统一解决方案,可无缝适配其xSPI + eMMC组合控制器IP,完美兼顾两种闪存的核心优势。

Arasan xSPI + eMMC组合PHY IP

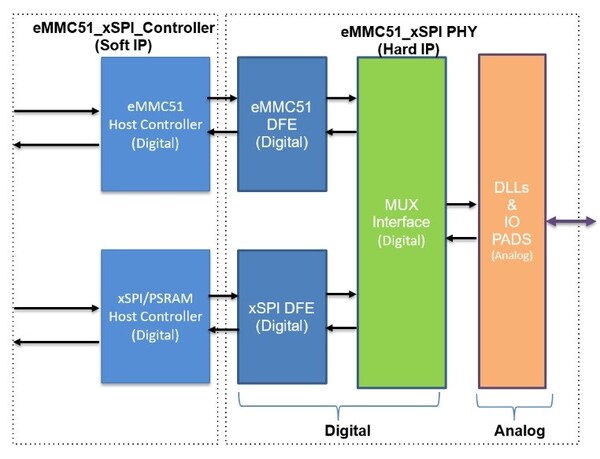

xSPI + eMMC组合PHY IP旨在满足嵌入式及启动应用对高性能、小面积存储解决方案日益增长的需求。 通过采用共享I/O与模拟前端架构,该设计显著减少了引脚数量与硅片面积,为SoC及MCU平台提供了兼具高性价比与功耗优化优势的实现方案。

Arasan销售副总裁Ron Mabry表示:“这款双模PHY使客户能够通过单一低引脚数IP无缝支持eMMC与下一代xSPI设备,从而降低系统成本并加速产品上市。 随着xSPI + eMMC组合PHY IP的推出,Arasan持续推动存储接口IP创新的边界。”

作为eMMC与xSPI IP领域的领军者,Arasan凭借全面的移动存储IP布局、超过200份eMMC IP授权的市场积淀,以及对行业需求的深刻洞察,通过这款双模PHY IP进一步完善了整合式存储解决方案,持续推动存储接口IP的创新边界。目前该IP已在28nm至3nm节点的领先晶圆代工厂开放授权,未来有望广泛赋能国防、航空航天、医疗等关键领域,助力相关行业SoC设计实现成本降低与产品上市加速的双重突破,为嵌入式及启动应用的存储升级提供有力支撑。