【导读】西部数据近日发布了基于RISC-V指令集的自研通用架构SweRV。SweRV内核是西部数据的几个RISC-V项目之一,作为他们努力引领ISA(指令集架构)及其生态系统的一部分,还是他们向免授权CPU核心过渡的一部分。

西部数据(Western Digital)近日发布了基于RISC-V指令集的自研通用架构SweRV。SweRV内核是西部数据的几个RISC-V项目之一,作为他们努力引领ISA(指令集架构)及其生态系统的一部分,还是他们向免授权CPU核心过渡的一部分。

基于RICS-V更开放的目标,SweRV的发布意味着第三方可以在自己的芯片设计中使用它,这不仅能推广特定的核心设计,还能推广RISC-V架构。

西部数据的RISC-V SweRV核心的RTL设计现在可以在GitHub上下载。该设计有Apache 2.0许可证,该许可证非常宽松(和非copyleft),允许核心免费使用,无论是否经过修改,无需任何修改即可以实物发布。

实际上,该许可证的要求非常少, 除了要求适当的属性外,唯一的显著限制是第三方开发商不能给他们的产品打上西部数据的商标。

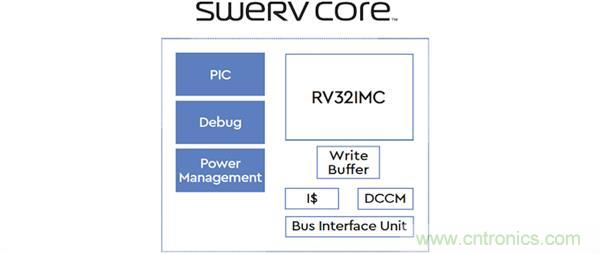

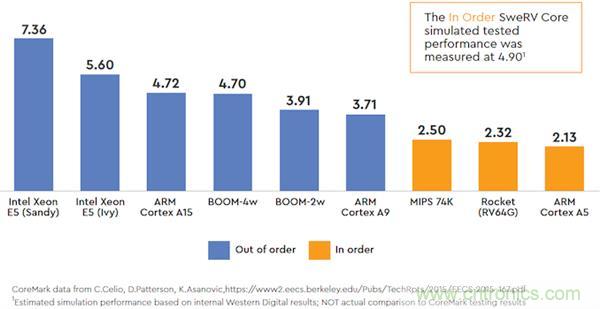

西部数据的SweRV架构是一个32bit顺序执行架构,具有双向超标量设计和9级流水线,采用28nm工艺技术实现,运行频率达1.8GHz,可提供4.9 CoreMark/MHz的模拟性能,略高于Arm的Cortex A15架构。

该核心的开发人员计划将其RISC-V内核用于西部数据的嵌入式设计,例如闪存控制器和SSD,但目前还不清楚何时投入使用。

作为RISC-V的主要支持者之一,西部数据认为,第三方使用其核心将有助于推动硬件和软件设计人员采用RISC-V架构,这将确保西部数据未来的设计能获得软件开发人员更好的支持。

随着RISC-V架构支持者越来越多的产品发布,是否意味着这个开源指令集架构(ISA)可以作为ARM和x86作为主处理器的替代品?

eetimes的作者Rick Merritt给出了肯定的答案,并指出了RISC-V还需要解决的问题。

Rick Merritt认为RISCV会成为Arm和x86作为主处理器的替代品,但还需要几年的时间。其中一个问题是尽管ISA已经稳定数月,但仍未获得正式批准。这是整个核心的规范,不过会有一些其它关键规格可能在今年获得批准。一旦规范获得批准,RISC-V基金会将会确定合规性测试的细节,企业可以通过测试以证明他们的产品符合规格。

另一个问题就是软件,RISC-V基金会刚开始研究Linux启动规范OpenSBI 0.1。除了Linux,Android,Windows或其它商用操作系统都没有端口。

Jon Masters还特别指出,操作系统端口只是软件冰山的一角。过去9年,他一直致力于标准版支持Arm服务器的红帽Linux。到目前为止,只有两个商用系统已经通过认证可以运行。

不过,RISC-V的支持者表示,开源架构背后有不断增长的100多个组织正逐步解决软件问题。与此同时,个人支持者也在进行多方面的努力,包括LLVM编译器和更多RTOS支持,预计很快将公布。

到目前为止,除了西部数据,NVIDIA也计划在其SOC中使用RISC-V控制器,Microsemi将在新的FPGA也使用它。另外,初创公司Abee Semi的RISC-V SoC获得约2000万套的订单,用于智能手表与健身手环。