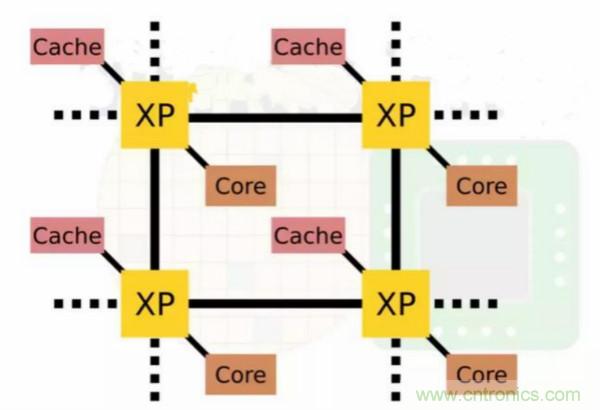

【导读】近日Arm宣布了一款有趣的测试芯片的投片。在深入研究芯片本身之前,有必要重点介绍一些即将达到交叉口的先进技术。早在2016年,Arm宣布了CMN-600技术,CNM代表coherent mesh network,也就是相干网状网络,这是从较早的CCN-500,也就是基于缓存相干网络转向网状互连的基础。CMN-600体系结构包括称为交叉点(XP)的网络路由器网格。每个XP均以2D网格扩展到其他XP。另外,每个路由器最多连接两个兼容AMBA CHI(一致性集线器接口)的设备。对于Arm最近发布的Neoverse N1之类的东西,它是系统缓存和核心的一部分。

为了帮助传统的硅芯片微缩,3D IC已经成为一种可行的的方法。传统将芯片核连接在一起的当前方法利用了诸如微凸点(micro-bumps)之类的机制,但这种做法加工过程复杂,且存在翘曲,应力,散热和性能问题,无法很好地扩展芯片的规模。为了解决这个问题,业界提出了Hybrid bonding(混合键合)技术。Hybrid bonding(也称为DBI)一直是半导体行业的长期目标。Hybrid bonding是传统热压键合(TBC)3维集成电路技术的有希望的替代方法。这是一种高度对齐精确的高精度键合技术,可以实现亚微米级间距键合的直接铜对铜和氧化物对氧化物键合。

最后一部分是新兴的存储技术,例如ReRAM和MRAM,它们可以用作高密度的片上非易失性存储或较慢的缓存。

Trishul测试芯片

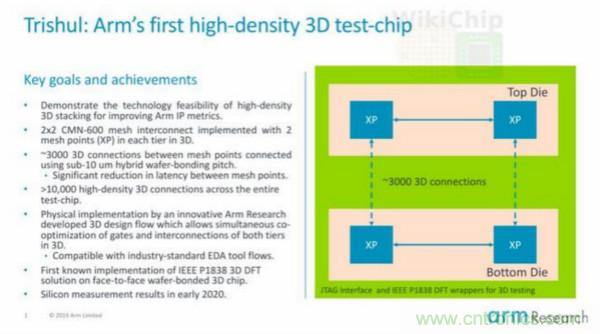

以上所有技术的实现结果,就是Arm的首款高密度3D测试芯片Trishul。GF利用相关技术与Arm合作推出测试芯片,希望该芯片能够使下一代高性能计算应用(例如AI)具有更高的集成度,尤其是在芯片的立体堆叠方面。

该测试芯片是在GlobalFoundries 12纳米(12LP)工艺上制造的。该芯片使用4个路由器集成了Arm的CMN-600网状互连。但是与传统芯片不同,在该测试芯片上,一个裸片上有两个以2D连接的路由器,而另一个裸片上有两个以2D连接的路由器。然后将两个管芯堆栈在一起,并且每个路由器也连接到相对管芯上的路由器。换句话说,该芯片是CMN-600技术推出后第一个实现3D网格互连的成品。

这两个芯片通过具有小于10 um键距的Hybrid bonding连接在一起,与当前的面对面micro-bumps密度相比有了很大的提高。从理论上讲,这可以使GF扩展到每平方毫米数百万个3D连接。虽然在该测试芯片上还没办法实现,但已经比当前的封装技术要密集得多。该芯片在每个路由器之间具有大约3000个3D连接,整个芯片上总共有10,000个3D连接。

密集的3D连接可实现更低的电容和更低的延迟。它们可用于最小化路由路径。 与某些新兴技术(例如ReRAM和MRAM)相结合,新的体系结构改进可能来自将某些类型的数据直接存储在处理元素上方。

除了芯片的技术功能之外,该测试芯片还是IEEE P1838 3D DFT的第一个已知实现,IEEE P1838 3D DFT是一种IEEE设计用于测试(DfT)的体系结构标准,允许在芯片堆栈上下发送测试控制和数据信号,以用于高效的测试。

GF希望使用3D连接提供10um和10um以下的间距互连。GF表示,他们的Hybrid bonding技术每mm2最多能够进行100万个3D连接。这需要1um的间距键合,只要可以通过市售的晶圆对晶圆键合工具即可实现极高的对准精度。

该测试芯片的硅测量结果将于2020年初提供。GlobalFoundries预计12LP混合键合将在2020年达到合格要求,并于2021年投入生产。

推荐阅读: