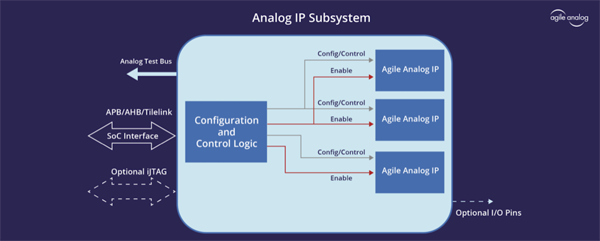

【导读】可定制的模拟IP公司Agile Analog推出了其首个模拟子系统系列,涵盖电源管理、PVT检测和睡眠管理。这些创新的数字封装子系统允许将多个模拟IP直接放入数字设计流程中,并通过标准外设总线(如AMBA APB)连接,从而显著减少了将多个模拟IP集成到任何ASIC中所需的工作量。这些子系统看起来就像一个普通的数字IP块,具有工程师期望的标准接口,使其易于理解和处理。

显著降低模拟 IP 集成工作量和成本

可定制的模拟IP公司Agile Analog推出了其首个模拟子系统系列,涵盖电源管理、PVT检测和睡眠管理。这些创新的数字封装子系统允许将多个模拟IP直接放入数字设计流程中,并通过标准外设总线(如AMBA APB)连接,从而显著减少了将多个模拟IP集成到任何ASIC中所需的工作量。这些子系统看起来就像一个普通的数字IP块,具有工程师期望的标准接口,使其易于理解和处理。因此,上市时间、成本和风险都大大降低了。最初,该公司正在推出三个子系统:用于电源管理的agilePMU,agilePVT - PVT传感器和用于睡眠管理的agileSMU。

Agile Analog产品营销总监Chris Morrison表示:“我很高兴地宣布我们的前三个子系统。客户一直在寻找缩短上市时间、降低成本和减少风险的方法,而我们新的数字包装子系统正是这样做的。至关重要的是,客户不再需要处理模拟和数字之间复杂的混合信号边界,从而大大减少了他们的设计工作,并降低了通常与集成复杂模拟IP阵列相关的风险。

子系统中的IP模块全部来自Agile Analog现有的可定制模拟IP产品组合。这允许子系统中的每个模块都可以根据客户的确切要求进行定制,同时位于整个数字包装中。与所有Agile Analog IP 一样,数字封装子系统与工艺和代工无关,并且每个设计都针对客户的特定 PDK 进行了优化。在子系统中集成 IP 可消除重复的模拟功能、降低设计规则检查 (DRC) 要求并优化互连,从而进一步增强客户的设计。这些可提高抗噪性、降低功耗和减小面积。

客户的另一个关键好处是,模拟到数字、混合信号、边界的所有验证要求都由敏捷模拟执行。这大大减少了客户设计和验证时间,降低了设计过程的风险,降低了混合信号设计工具的许可成本,并简化了集成。客户现在可以添加模拟功能以提供产品差异化,而无需专业的模拟和混合信号工程师以及相关的昂贵工具链。

Agile Analog的子系统提供了一整套支持资料,包括System Verilog模型,可轻松集成到客户现有的数字验证流程中。

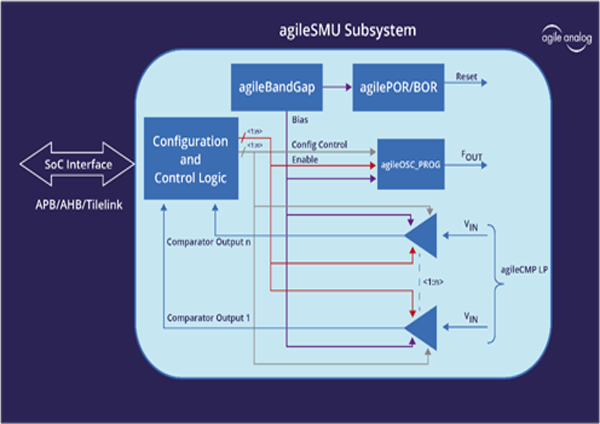

agileSMU Sleep Management Subsystem

agileSMU睡眠管理子系统

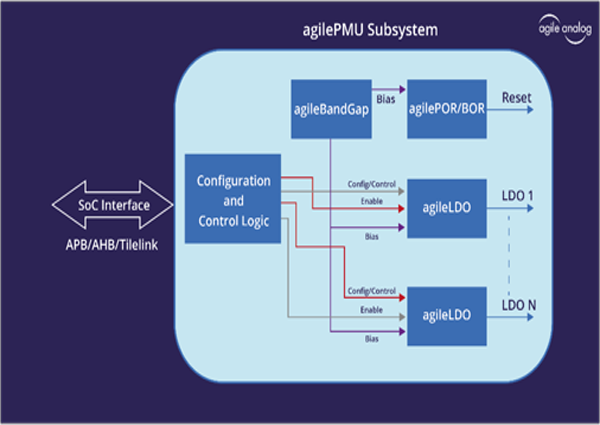

agilePMU 子系统是面向 SoC/ASIC 的高效且高度集成的电源管理。具有上电复位、多个低压差稳压器和相关的基准发生器。agilePMU子系统旨在确保低功耗,同时提供最佳的电源管理功能。agilePMU子系统配备集成数字控制器,提供对启动和关断的精确控制,支持电源排序,并允许为每个LDO提供单独的可编程输出电压。状态监视器提供有关子系统当前状态的实时反馈,确保最佳系统性能。

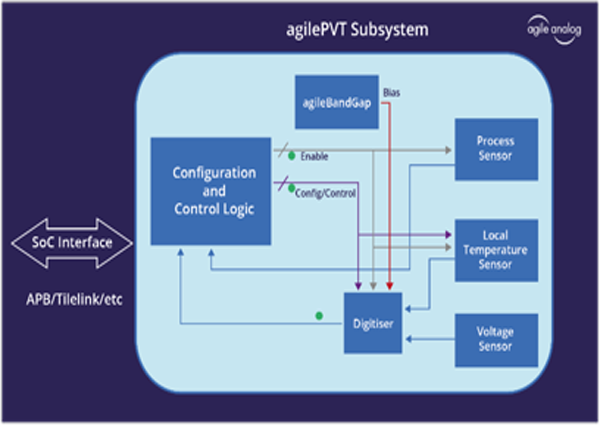

agilePVT传感器子系统

监控工艺、电压和温度变化对于优化现代 SoC/ASIC 的功率和性能至关重要,尤其是对于高级节点和 FinFET 工艺。agilePVT 传感器子系统是一个低功耗集成宏,由过程、电压和温度传感器以及相关的参考发生器组成,用于片上监控器件的物理、环境和电气特性。agilePVT 子系统配备集成数字控制器,可精确控制启动和关闭。状态监视器提供有关子系统当前状态的实时反馈,确保在整个产品生命周期内实现最佳系统性能。

agileSMU睡眠管理子系统

agileSMU 子系统是一个低功耗集成宏,由安全管理从睡眠模式唤醒 SoC 所需的基本 IP 模块组成。 通常包含一个用于低频 SoC 操作和 RTC 的可编程振荡器、多个可用于启动唤醒序列的低功耗比较器,以及一个为 SoC 提供稳健的启动复位的上电复位。 agileSMU 子系统配备集成数字控制器,可精确控制唤醒命令和排序。状态监视器提供有关子系统当前状态的实时反馈,确保在整个产品生命周期内实现最佳系统性能。

Agile Analog正在通过其创新的、可配置的多进程模拟™ IP 技术 Composa™ 改变模拟 IP 的世界。Agile Analog 总部位于英国剑桥,在全球拥有越来越多的合作伙伴和客户,Agile Analog 开发了一种独特的方法来自动生成模拟 IP,以满足客户在任何代工厂的几乎任何工艺上的确切规格。该公司为电源管理、数据转换、IC运行状况和监控、安全性和始终在线域提供广泛且不断扩展的模拟IP和子系统选择。Agile Analog的新方法利用其Composa库中久经考验的模拟电路来创建定制和验证的模拟IP解决方案。这缩短了上市时间,提高了质量,有助于加速半导体设计的创新。

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理。

推荐阅读:

意法半导体STM32全面支持Microsoft Visual Studio Code

玛斯柯采用艾迈斯欧司朗LED解决方案,为雷根斯堡棒球体育馆提供照明体验

COSEL推出新型无风扇传导冷却式三相高效电源HCA3500TF

意法半导体推出功率量程更大的STM32 烧录调试器,赋能下一代超低功耗应用